Serial 2 S Complementer Shift Register

Arch #11 Computer Architecture Start Lecture #11 Homework: Read 3.1-3-4 3.1: Introduction I have nothing to add. 3.2: Signed and Unsigned Numbers MIPS uses 2s complement (just like 8086) To form the 2s complement (of 0000 1111 0000 1010 0000 0000 1111 1100) • Take the 1s complement. • That is, complement each bit (1111 0000 1111 0101 1111 1111 0000 0011) • Then add 1 (1111 0000 1111 0101 1111 1111 0000 0100) Need comparisons for signed and unsigned. • For signed a leading 1 is smaller (negative) than a leading 0 • For unsigned a leading 1 is larger than a leading 0 Comments on Two's Complement You could easily ask what does this funny notation have to do with negative numbers. Let me make a few comments. • What does minus 1 mean?

Ans: It is the unique number that, when added to 1, gives zero. • The binary number 1111.1111 has this property (using regular n-bit addition and discarding the carry-out) so we do seem to have -1 correct. • Just as n+1 (for n≥0) is defined as the successor of n, -(n+1) is the number that has -n as successor. That is we need to show that TwosComp(n+1) + 1 = TwosComp(n). • This would follow if we coud show OnesComp(n+1) + 1 = OnesComp(n), i.e, (n+1)' + 1 = n'. • Let n be even, n = *0, * arbitrary.

Design an 8 bit serial 2’s complementer with a shift register and a flip‐flop. The binary number is shifted out from one side and its 2’s complement shifted into the other side of the shift.

• Write n', n+1 and (n+1)' and see that it works. • Let n be odd, n = *01 s1, where 1 s just means a bunch of ones. • Again it works. • So for example TwosComp(6)+1=TwosComp(5) and hence TwosComp(6)+6=zero, so it really is -6. Sltu and sltiu Like slt and slti but the comparison is unsigned. Homework: 3.1-3.6 3.3: Addition and subtraction To add two (signed) numbers just add them. That is, don't treat the sign bit special.

To subtract A-B, just take the 2s complement of B and add. An overflow occurs when the result of an operation cannot be represented with the available hardware. For MIPS this means when the result does not fit in a 32-bit word.

• We have 31 bits plus a sign bit. Free download neurology img friendly residency programs list programs. • The result would definitely fit in 33 bits (32 plus sign) • The hardware simply discards the carry out of the top (sign) bit • This is not wrong--consider -1 + -1 11 (32 ones is -1) + 11 ---------------------------------- 110 Now discard the carry out 10 this is -2 • The bottom 31 bits are always correct.

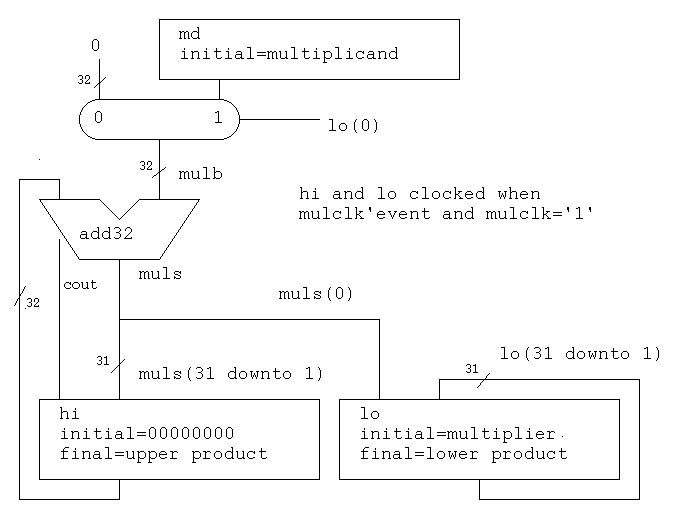

Overflow occurs when the 32 (sign) bit is set to a value and not the sign. • Here are the conditions for overflow Operation Operand A Operand B Result A+B ≥ 0 ≥ 0 64 multiplier.

What about the control? • Always give the ALU the ADD operation • Always send a 1 to the multiplicand to shift left • Always send a 1 to the multiplier to shift right • Pretty boring so far but • Send a 1 to write line in product if and only if LOB multiplier is a 1 • I.e. Send LOB to write line • I.e. It really is pretty boring This works! But, when compared to the better solutions to come, is wasteful of resourses and hence is • slower • hotter • bigger • all these are bad An Improved Circuit The product register must be 64 bits since the product can contain 64 bits.